# A Innovative Method for Analysis of Faults Caused At Multiple Locations

# Shahul Hameed Jamshak<sup>1</sup>, James Akash<sup>2</sup>

<sup>1,2</sup>Dept. of ECE, RAJADHANI INSTITUTE OF SCIENCE AND TECHNOLOGY, Kerala, India.

#### To Cite this Article

SHAHUL HAMEED JAMSHAK, JAMES AKASH, "A Innovative Method for Analysis of Faults Caused At Multiple Locations", International Journal of Scientific Research in Engineering & Technology, Volume 02, Issue 02, March-April 2022 PP: 09-10

Abstract: Testing is a critical early push toward plan of VLSI. With an enormous number of semiconductors being facilitated in one chip, multiple lacks could exist. To unequivocally and successfully separate the deficiency regions, a 3D square based EPP assessment system isproposed. The decided rate tends to the EPP of the implanted issue. In the circuit, the strong shape potential gains of region at theinitial stages are changed and the bumble not set in stone. This is done until the botch count diminishes to nothing. Both the techniquesareapplied to ISCAS '89 benchmark circuits and the parameters, for instance, area, speed and power are computed. Itcan be observed that the district and power are diminished incredibly by EPP procedure appeared differently in relation to FEG technique and the speed increasesapproximatelyby 7times. The results show that the EPP method is more advantageous than the graph-based approach.

Expressions — fault to learner, reliability, probability-based, multiple fault diagnosis.

#### **I.INTRODUCTION**

Foundation In the improvement of facilitated circuits, testing is done to recognize lacking chips. Testing is moreover completed to dissect the support for achip dissatisfaction to additionally foster the gathering framework. Testing an electronic circuit incorporates applying a fitting plan of inputpatterns to the circuit and checking for the right outcomes. In any case, basic individual test (BIST) techniques have been made inwhich a piece of the analyzer capacities are coordinated on the chip enabling the chip to test itself. BIST gives different outstanding advantages. It gets rid of the prerequisite for exorbitant analyzers. It gives speedy area of besieged units in a system considering the way that the chipscantestthemselvesconcurrently. Theincreasing pincount, operating speed, and complexity of IC's isoutstripping the capabilit ies of external analyzers. BIST gives deals with these issues. Fig. 1. is a block frame showing the plan for BIST. The circuit that is being attempted is known as the circuit-under-test (CUT). There is a test plan generator which applies test guides to the CUT and an outcome response analyzer which truly checks the outcomes out. The test plan generator ought to make a lot of test plans that provides high fault coverage in order to thoroughly test the CUT.

## II. EPP BASED APPROACH

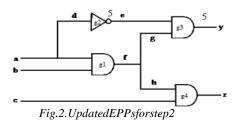

To accurately and efficiently evaluate theerrorpropagation probability, we propose a cube-based EPP analysis technique. Percentage tends to the EPP of the injected weakness. Monte Carlo reenactment is significantly precise yet very monotonous because it needs to deal with the whole data set for every deficiency to get an EPP. As such, existing Monte Carlo reenactment strategies have totrade off precision against computational complexity on the other hand; static assessment uses the probability speculation to en roll EPPs. Fig. 2.provides an example for an example of using cubes and covers.

The enrolled EPP values uncover that the scores are high at entrances g1 and g4. Thusly, these two entrances are to be considered for theinversion 3D shape procedure in the accompanying stage. While adjusting the 3D squares, the mix-up count seems to vary. If the goof count tends to reducethen the entryway is recorded as a defective part. Else the entrance is stayed away from concerning thought. The EPP score is then revived and the procedure continued until the error countiszero.

ISSN No: 2583-1240

| a | b | С | y   | Z        |

|---|---|---|-----|----------|

| 0 | 0 | 0 | /1\ | 0        |

| 0 | 0 | 1 | 1   | 1        |

| 0 | 1 | 0 | 1   | 0        |

| 0 | 1 | 1 | \1/ | $\Theta$ |

| 1 | 0 | 0 | 0   | 0        |

| 1 | 0 | 1 | 0   | (1)      |

| 1 | 1 | 0 | 0   | 0        |

| 1 | 1 | 1 | 0   | (0)      |

Fig. 1. Truthtable after inversion in step 1

Consequently, the entryway g1 and g4 are with no slip-up. In the accompanying stage, EPPs are to be reassigned ignoring the entryways eliminatedduring the stage 1. In the accompanying stage, simply a solitary way exists between the fundamental information and the outcome, a-d-e-y. The invigorated EPP is giveninFig. 9.

Taking entryways g2 and g3 for this step, reality table gets changed which seems to be the table in Fig. 9. Along these lines, it might be shut thatthe botch is accessible in the manner between fundamental data 'a' and fundamental outcome 'y', through way a-d-e-y. Subsequently, there is a faster andeasieridentification of the solution.

#### **III.CONCLUSION**

The different weaknesses were distinguished using other existing systems and the results were contemplated. Later on, another single cycle access test structure for reasoning test. It will kills the silly one of a kind power use issue of standard shift-based really look at chains during trading progress in the result FF and besides diminishes the getting to time into one clock cycles. This leads to more sensible circuit direct during stuck-at and at-speed tests. It enables the all out test to run at much higher frequencies equalor close to the one in functional mode. In this work multifaceted design will be extended straightly with arrangement level. To hold the design complexity by grouping the design unitsasavarious independent pages and accessing will be carried out by selecting pages.

### **REFERENCES**

- [1] Xiaochun Yu and R. D. (Shawn) Blanton (2008), "Multiple Defect Diagnosis Using NoAssumptions on Failing PatternCharacteristics", DAC, California, pp.361-366.

- [2] Rodríguez-Montañés. R, Arumí, D, Figueras S. Einchenberger, Hora. C, Kruseman .B(2010), "DiagnosisofFullOpenDefectsinInterconnect Lines withFan-out", IEEE, pp. 233-238.

- $[3] \ Yung-Chieh Lin and Kwang-Ting Cheng (2006), ``Multiple-Fault Diagnosis Based on Single-Fault Activation and Single-Output Observation'', EDAA.$

- [4] Yung-ChiehLin, FengLuandKwang-TingCheng(2007), "Multiple-

- Fault Diagnosis Based On Adaptive Diagnostic Test Pattern Generation", IEEE Transactions.

- [5] Jing Ye,YuHu,XiaoweiLi,Wu-Tung Cheng,YuHuang andHuaxing Tang (2014), "Diagnose Failures Caused by Multiple Locations at a Time", IEEE Transactions.