Volume 1, Issue 3 (May-June 2021), PP 01-03 www.ijsreat.com

# **Investigation on Reversible VM Using Cadence Technology**

### S.Tharunya<sup>1</sup>, Deepika Rani Sona<sup>2</sup>, Kalapraveen Bagadi<sup>3</sup>

<sup>1,2,3</sup>Department of Information Technology, VelTechRangarajanDrSagunthala R&D Institute of Science and Technology, India.

Abstract: Vedic science is a dated method of Indianarithmeticasitcontains 16Sutras. Afast 16\*16multiplier configuration is arranged utilizing Urdhva Tiryak bhyam sutra is introduced in this work. By utilizing this sutrathefractional items and totals are made in single stage which reduces the structure of plan in processors. By utilizing this method we can diminish the delay furthest extent when contrast with cluster or corner multiplier. By utilizing this strategy we less enthein citing concede in regards to pack based plan and parallel carry based use which are most normally used models. The essential significance of this paper is the delay and dynamic power usage is found to be diminished.

**Keywords:** Wallacetreemultiplier, Vedicmultiplier (VM), Reversible logic.

### I. INTRODUCTION

Augmentationisacentralcapacityinmathactivitiesdependent on a couple of tasks. Adders structure the fundamentalbasic plan of the multiplier. Generally allowance is atwo'scomplementaddition. These arithmetic operations should be acted in the At high speedapplications. the point when these assignments highspeed, then they can be used to speed up the operations of the complicated circuits. So designing the efficient adder is in the front Further in view of the progress in the technology, several limits like wire length, number of fan outs arealso considered. Reversibility in dealing with suggests that no data about the computational states can ever belost, so we can recuperate any prior stage by enrolling in reverse theoutcomes. This is named as logic reversibility. The condition of information sources can be recuperated from the outcomes by using theconceptofreversiblelogiccomponents. This reversible logic is used in adders and reversible adders are arranged. TheadderblockintheVedicmultiplierarereplacedby thisreversibleadderstoformthereversibleVedicmultiplier(VM).

### II. VEDICMATHEMATICS

Theutilization of Vedicscience isto decreases the regular figuring "sintraditional science to exceptionally basic one. It additional lygives via ble calculations that to be connected to different parts of designing, for example, registering.

### A. UrdhvaTiryakbhyamSutra

"UrdhvaTiryagbhyam" sutra is used in our proposedVedic multiplier [3]. The increment of any two decimalformatted factors is performed by using this sutra. Thissutra works in both across and vertical heading. Thissutra is one among the 16 sutras and relies upon the ancientvedic math. Here all of the midway things generationand the development happen at the same time.

Further

this

sutra isbasedontheadditionequationwhichisutilizedforthemultiplication.Becauseofitsnormalschematic,ittendstobeeffectively plan in CPUs and coordinators can withoutmuch of a stretch diversion these issues to keep a strategicdistancefromcalamitousgadgetdisappointments.TheVedicmultiplier (VM) module for different pieces is gotten a handle on asbelow.

### B. VMfor 2\*2 piece Module

The action of 2\*2 VM where the 2-digit numbers X and YareX=x1x0 and Y=y1y0. The minimum noteworthy bits are replicated which gives the base enormous piece of the last item (vertical). At that point, the multiplicand (LSB) is duplicated with the following multiplier upper piece and included with, the result of multiplier LSB and next multiplicand (across) Upper piece. The method goes on in a similar way. The practical plan of the horrible VM is given in the following equations.

#### III. REVERSIBLEGATES

An information and n yield reasoning is utilized in reversiblegate. Therepresentation is called a sone to one mapping. The outputs can in any case hanging out there from the information sources meanwhile the inputs can also be obtained from the outputs. Since one to many thought isn't reversible, direct fan out isn't allowed during the combination of reversible circuits. Anyway we can achieve the fan out in the reversible circuits by utilizing additional entrances. While arranging the reversible circuit we must keep an eye out for using the amount of reversible

### International Journal of Scientific Research in Engineering & Technology

logicgatestobeminimum. The complexity and the performance of the circuit are determined by number of factors.

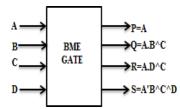

### A. BMEGate

BMEisa4\*4reversiblegate.Ithasfourinputsandfouroutputs.Theinformation is given by i(A,B,C,D) and theresponse is tended to by o(P,Q,R,S). The outcome is definedby  $P=A,Q=AB^{C},R=A.D^{C}$ and $S=(A^{B}^{C},D)$ . Figure 4 shows the block diagram of BME entrance. Figure 5 shows theschematicofBME reversible entrance.

BlockdiagramofReversibleBME gate

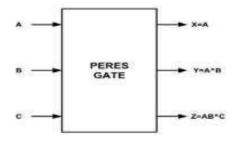

#### B. PeresGate

$One form of 3*3 reversible entry way is the Peresgate. It has three informations our cesand three output responses. The illustration of Peresentry way is indicated below in the Figure 6 and Figure 7 shows the schematic of reversible Peresgate by using Cadence instrument. The response is given by A, Y=A^B,Z=AB^C. Peresgate has the Quantum cost of five.$

Block diagram of Reversible Peres Gate

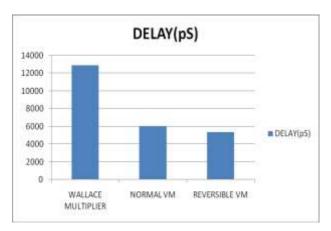

### **VI.RESULTSN**

Table I shows the comparison result of different multipliers. It is generally noted that the VM has lowest delay and low power when diverged from various kinds of multipliers. But when reversible reasoning is applied to this multiplier, it is seen that the power and delay are also decreased. The deferral is reduced by 11.13% and the power is reduced by 22.54%. Figure 10(a) and Figure 10(a) shows the pictorial representation of the comparison result. Simulations are performed using Cadence 45 nm technology.

Delaycomparisonofdifferentmultipliers

### REFERENCES

1. Rakshith S, Rakshith T, "Optimized Reversible Vedic Multipliers

## International Journal of Scientific Research in Engineering & Technology

- $for low power operations ``IEEE Conference on Information and communication\ Technologies, 2013.$

- Thapliyal, HandSrinivas, M, B, "NovelReversibleMultiplierArchitectureUsingReversibleTSGGate", ProceedingsonIEEEInternationalCo nferenceonComputerSystemsandApplications,2006,pp.100-103.

- Shams, M, Haghparast, M and Navi, K, "Novel Reversible Multiplier Circuit in Nanote chnology", World Applied Science Journal, Vol. 3, No. 5, 2008, pp. 806-810.

- Kotilakshmi, Santhoshkumarand Rameshwar Rao, "Implementation of Vedic Multiplier Using Reversible Gates", International Conference on Computerscience and Information Technology, 2015, pp 125-134. Vijay K Panchal and Vimal H Nayak, "Analysis of multiplier

- circuitusingreversiblelogic,,,InternationaljournalforInnovativeResearchinScienceandTechnology, Vol1, Issue6,Nov2014.

- 6. Ratna Raju et.al.," A High Speed 16\*16 Multiplier Based on UrdhvaTiryakbhyam Sutra", International Journal of Science Engineering and Advance Technology, Vol 1, Issue 5, 2013.